製品情報

半導体テストのご提案

半導体テスト用プリント配線板

進化し続ける半導体技術。ウェハーサイズの大型化、多ピン化に対応した高多層・大型テスト基板の高精度加工技術。伝送信号の高速化に対応する高品位電気特性要求。パッケージの小型化に対応する高精度微細加工技術などが求められています。

OKIサーキットテクノロジーは、進化し続ける半導体デバイスの確かな品質を、陰で支えている半導体テスト用基板をご提供いたします。

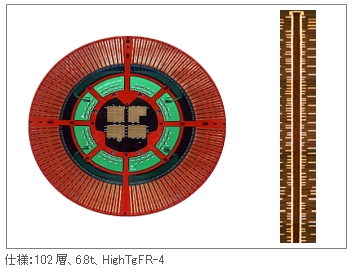

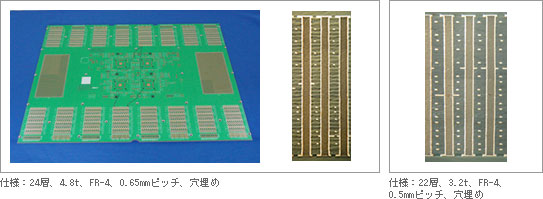

プローブカード

- 当社保有技術

- 半導体の微細化、多ピン化に対応した高精度、高多層基板をご提供いたします。

- 信号伝送の高速化による高品位電気特性に対応した、伝送線路シミュレーション技術

および特性インピーダンスの高精度コントロールを実現します。 - 同時並行設計、特別生産体制により、開発期間の短縮を実現します。

- 製品仕様

- 層数:4層~124層

- 最大サイズ:558×643mm

- 最大板厚:7.6mm

- 材料:各種低誘電率材料に対応可能

パフォーマンスボード・DUTボード

- 当社保有技術

- 半導体の微細化、多ピン化に対応した高精度、高多層基板をご提供いたします。

- 狭ピッチ化(0.30mmピッチ)に対応した、高アスペクト基板をご提供いたします。

- 信号伝送の高速化による高品位電気特性に対応した、伝送線路シミュレーション技術

および特性インピーダンスの高精度コントロールを実現します。 - 同時並行設計、特別生産体制により、開発期間の短縮を実現します。

- 製品仕様

- 最大サイズ:558×643mm

- 最大板厚:7.6mm

- 材料:各種低誘電率材料に対応可能

- BGA対応ピッチ:0.5mmP(貫通VIAφ0.20ドリル/板厚7.6mm)、0.4mmP(貫通VIAφ0.15ドリル/板厚6.35mm)、0.35mmP(貫通VIAφ0.15ドリル/板厚5.3mm)、0.3mmP(BVHφ0.10ドリル/BVH厚3.5mm)

- 0.30mmピッチ

- BVH厚:3.2mm

- ドリル径:φ0.10ドリル

- アスペクト比:32

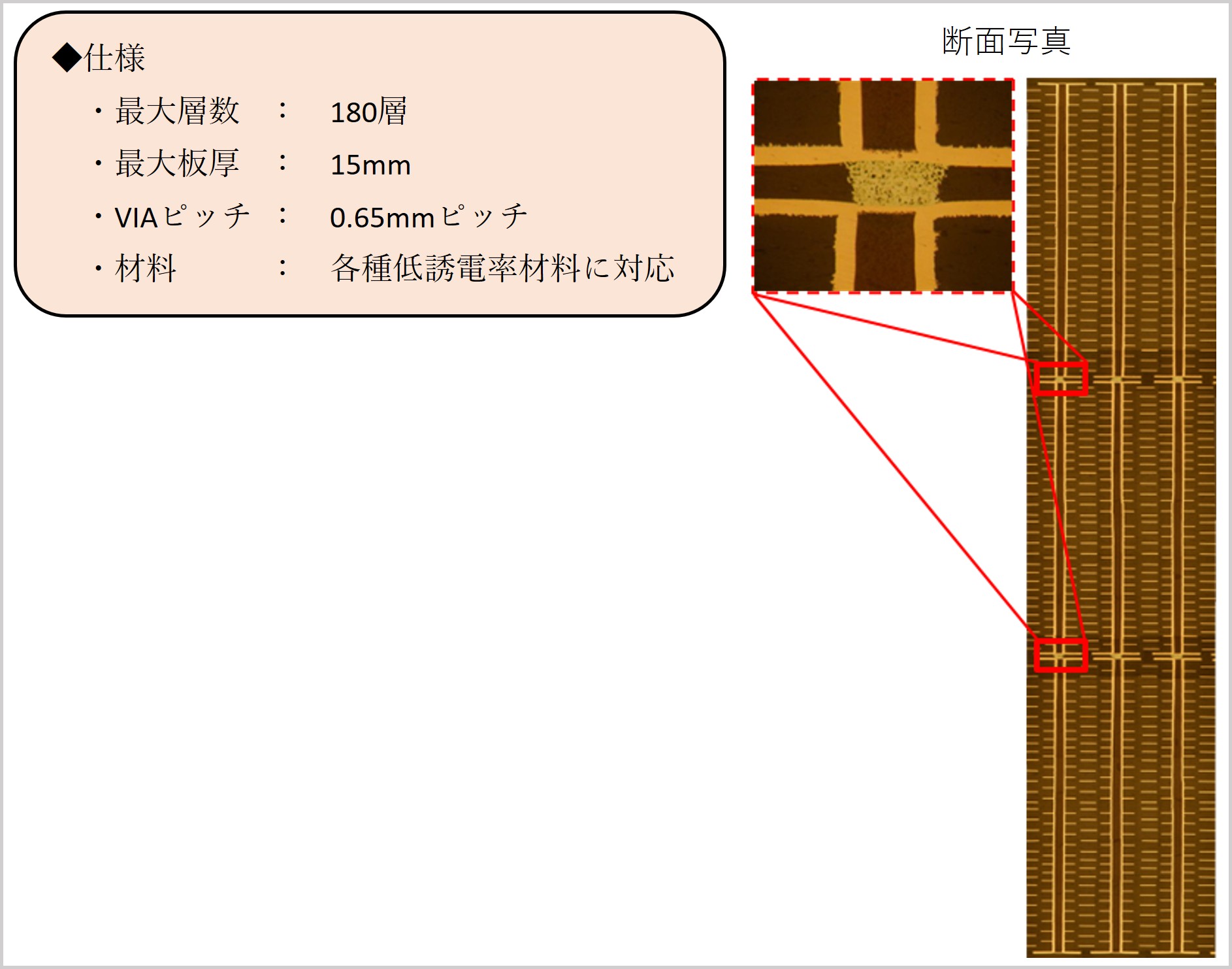

導電ペースト基板間ビア接続プリント配線板<180層・板厚15mm>

導電ペーストによる基板間ビア接続技術により、「最大層数:180層 最大板厚:15mm」の超高多層プリント配線板を実現

- 特徴

- 複数の多層プリント配線板を積層接続(表面のビアとビアを接続)し、超高多層プリント配線板を構成

- ドリル刃長や製造ラインの制約による従来の通常製造プロセスで可能であった「最大板厚:7.6mm」を超える超高板厚プリント配線板に対応

- 超高板厚化により、従来の通常製造プロセスで可能であった「最大層数:124層」を超える超高多層化にも対応

- 超高板厚化、超高多層化に加え、IVHとの併用で配線収容エリアの拡大が可能

- 主な適応例

- 半導体テスト装置、プローブカード

- 製品概要および仕様

- 基本仕様

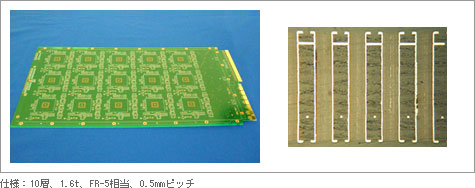

バーンインボード

- 当社保有技術

- 多ピン化(1,000ピンクラス)に対応した、高集積大型多層基板をご提供します。

- 狭ピッチ化(0.4mmピッチ)に対応した、高精度大型基板をご提供します。

- 製品仕様

- 層数:2層~16層

- 最大外形:482×623mm

- 板厚:1.6mm ~

- 材料:FR-4、HighTgFR-4

- 構成:SVH、穴埋め対応可

- ソケットピッチ:0.40mm ~

- 表面処理:無電解金めっき、ソルダーコート、銅スルー

- 関連するソリューション

- 関連する製品

- 関連するサービス