製品情報

製品紹介

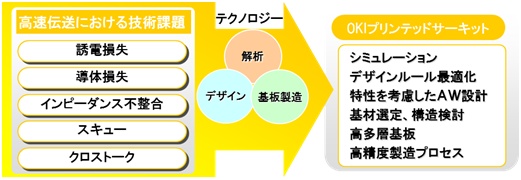

高速/高周波のご提案

超高速回路・高周波プリント配線板

GHz対応プリント配線板へ、最適Via構造を提供いたします。

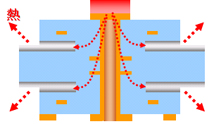

作用

信号配線の特性インピーダンス値とVia部の特性インピーダンス値の差を低減。

効果

- 信号の伝播速度の均一化

- 伝送線路の反射・減衰量を低減

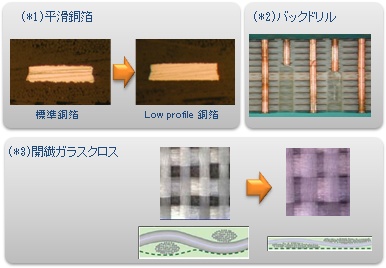

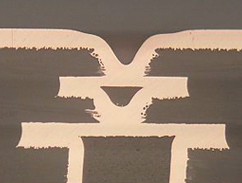

バックドリル工法の確立

高速伝送対応バックプレーン等、高板厚プリント配線板で活用。

Viaスタプ除去工法(バックドリル)の効果

TH実装コネクターの欠点を解消。

Viaスタプの電気特性への影響

Via部と配線の特性インピーダンス値の差が大きいほど反射・減衰量が増加する。

<配線条件>配線長=100mm、ビア個数=2個

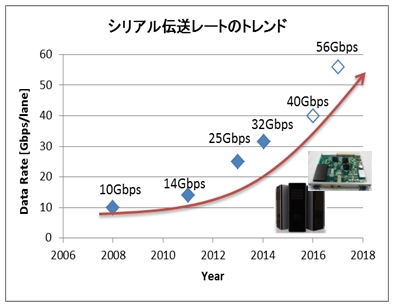

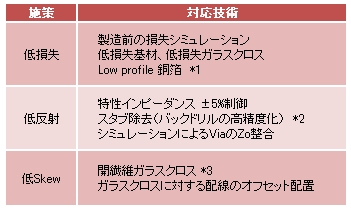

32Gbps高速伝送プリント配線板

(32Gbps High-speed transmission PCB)

デザイン、マテリアル、製造プロセスの追及により、

電気伝送による32Gbps/laneの高速伝送を実現

今後、40Gbps/laneを目指します

特長

- 各種シミュレーション、自社評価データより基板仕様検討をサポート

- 要求性能に対してミニマムコストとなる材料、構造、プロセスの提案

- 挿入損失の特性検査対応

主な適応例

- サーバー、ルーターなど情報通信機器

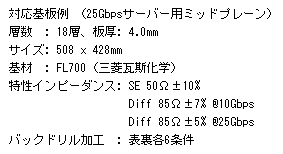

製品概要および仕様

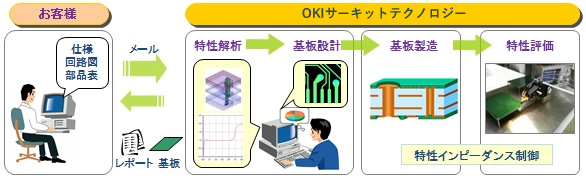

トータルインピーダンス制御プリント配線板

(Total impedance controlled PCB)

高速基板における伝送路全体のインピーダンス、遅延時間制御をワンストップで提供します

特長

- シミュレーションによりビア、パッドを含む伝送線路全体のインピーダンスを最適化

- 伝送線路のpsオーダーの遅延時間制御に対応

- 仕様、回路を提示いただくだけで要求特性を満足するプリント配線板を提供します

主な適応例

- 高速通信ボード(フロントカード、バックプレーン)

- 高板厚ボード(プローブカード、半導体テスターボード)

- 各種CPUボード:PCIE Gen2(8Gbps)、USB3.0(5Gbps)、DDR3など

製品概要および仕様

- DDR3メモリー搭載ボード

IVH(Interstitial Via Hole)基板

- [当社保有技術]

- Board type:BWB for press-fit,IC tester board,etc.

- Layer:upto 50

- Size:670 × 570mm max.Thickness:6.3mm max.

- Characteristic impedance control:+/-5%

- Material:FR-4,FR-5,BT,Polyimide,Low dk

- [製品仕様]

- Layer:20

- Structure:IVH,10+10

- Board thickness:3.2mm(.126")

- Board size:340 × 366.67mm(13.39" × 14.44")

- Line width/space OL:0.127/0.110mm(.005"/.0043")IL 0.1/0.114mm(.004"/.0045")

- Min. hole size(drill size)PTH:0.35mm(.0014").IVH 0.25mm(.001")

- Surface finish:HASL

- Material High Tg:FR-4

- Characteristic impedance:Single-end 50ohm+/-10%, differential 90ohm+/-10%

IVH 基板 - シーケンシャル積層

- [当社保有技術]

- Enables high layer count

- Enables various IVH connections

- Enables Characteristic Impedance Control

- [製品仕様]

- Number of layers:4 - 28 layers

- Board thickness:0.5(.020")to 4.2(.165")

- IVH diameter Minimum:0.2mm(.008")

- Minimum land diameter:(OL)0.5mm(.020")

- Minimum land diameter:(IL) 0.5mm(.020")

- Minimum line width:0.075mm(.003")

- Minimum line space:0.125mm(.005")

PAD on VIA 基板

- [当社保有技術]

- Capability of Resin-Filling

- [製品仕様]

- Board size 590 × 480 mm max.

- Board thickness 0.6 to 6.3 mm

- Hole size 0.35mm/6.3 mm thick0.2mm/3.5mm thick

- Pad-on-via OK

- Micro-via(bottomed)filling 0.13mm

ハイパーピア基板

- [製品仕様]

- Layer 16

- Laser micro via L1-2,L2-3

- Board thickness 2.1mm(.083")

- Board size 235 × 415mm (9.25" × 16.34")

- Line width/space 0.10/0.10mm(.004"/.004")

- Min. hole size(drill size)0.3mm(.0012")

- Surface finish Immersion silver

- Material High Tg FR-4

- Characteristic impedance 55ohm+/-10%

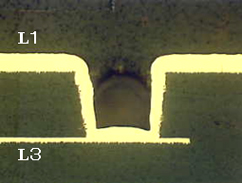

バックドリル基板

- [製品仕様]

- Layer 26

- Laser micro via L1-2,L2-3

- Board thickness 2.1mm(.083")

- Board size 235 × 415mm(9.25" × 16.34")

- Line width/space 0.10/0.10mm(.004"/.004")

- Min. hole size(drill size)0.3mm(.0012")

- Surface finish Immersion silver

- Material High Tg FR-4

- Characteristic impedance 55ohm+/-10%

高密度のご提案

高密度高機能部品の搭載、部品の小型化を実現したい

ビルドアップ構造あるいは極小穴あけ技術を用いて高密度狭ピッチ配線板をお届けします。

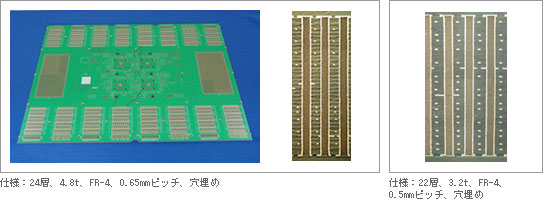

高密度狭ピッチ配線板

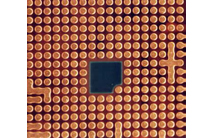

表面写真

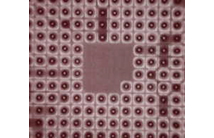

X線

スタックビア(L1-2-3)

スキップビア(L1-3)

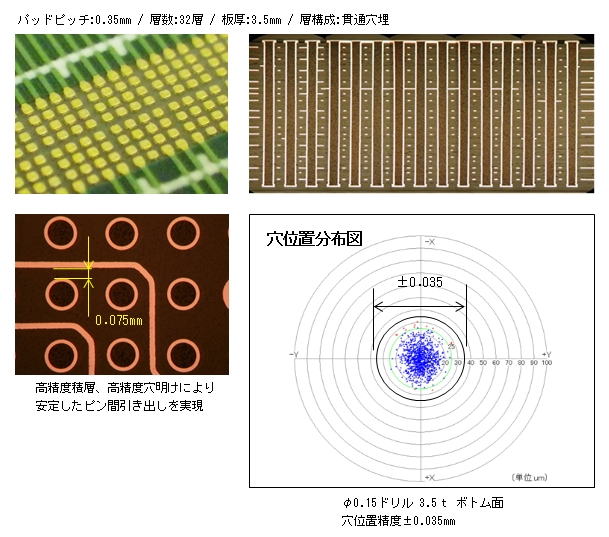

狭ピッチBGA/CSP対応プリント基板

(The PCB for Narrow pitch BGA/CSP)

FiTT(Fine pitch Through via Technology)工法により

0.35mmピッチ、1,000ピンBGA対応 32層プリント配線板を実現

特長

- 狭ピッチ、多ピン化が進む高機能半導体(0.35㎜ピッチ1,000ピンクラス)のテスター用基板など従来のビルドアップ工法では実現困難であった仕様に対応

- シンプルな貫通ビア構造であるため、短納期、低価格を実現

- 電源供給、グランド接続が安定的に確保できるため、半導体テスター用基板に要求される高い信号品質の確保が可能

主な適応例

- BGAパッケージのテスター基板

- ソケットボード、プローブカード等

製品概要および仕様

- 基本仕様

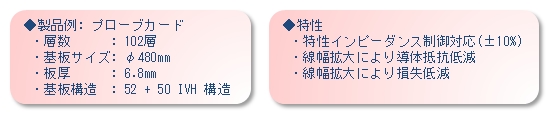

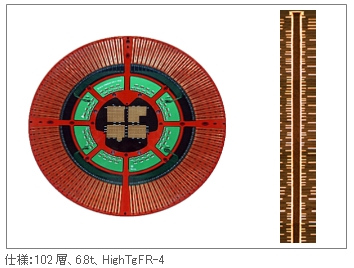

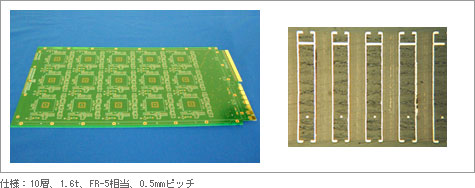

超高多層<100層超>リジットプリント配線板

(Over100Layer Advance Super Multi-layer Rigid PCB)

高TgFR-4を用いたリジッドプリント配線板で100層を実現

電気特性を確保しながら、高密度配線収容に対応

特長

- 高Tg FR-4を用いた通常製造プロセスで100層を超える高多層基板に対応

- IVH、ビルドアップ、貫通穴埋め等の様々なVIA構造を組み合わせることが可能

- 独自構造により特性インピーダンス制御と導体抵抗低減を実現

主な適応例

- 半導体テスト装置、プローブカード

製品概要および仕様

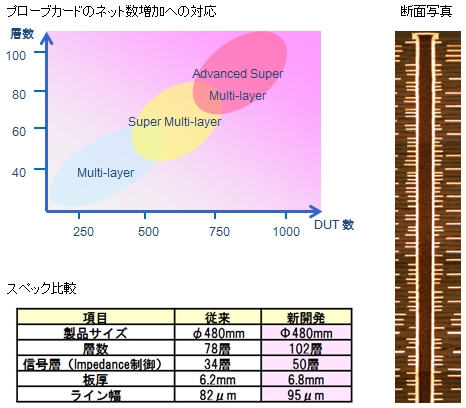

大電流/放熱のご提案

メタルコア・メタルベース搭載プリント配線板

メタルコア・メタルベースを搭載することで放熱性を高めるプリント配線板を提供します。

メタルベース

メタルコア

厚銅多層プリント配線板 厚銅エッチング技術、厚銅積層技術

特長

- 従来商品は銅厚が70µm程度であるのに対し、本製品は175~215µmの銅厚を有し、放熱特性が向上。

- 当社の高多層製造技術/IVH製造技術により、厚銅でのブラインドホール構造を実現。

製品仕様

5層IVH構造(下図参照)

対応例

- コンパクト電源

- 大電流用基板(10A以上)

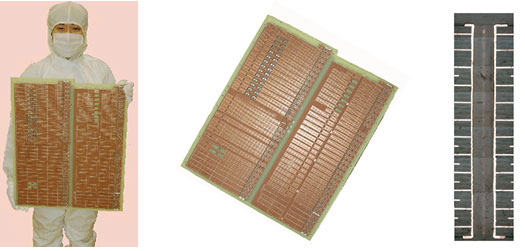

半導体テストのご提案

半導体テスト用プリント配線板

進化し続ける半導体技術。ウェハーサイズの大型化、多ピン化に対応した高多層・大型テスト基板の高精度加工技術。伝送信号の高速化に対応する高品位電気特性要求。パッケージの小型化に対応する高精度微細加工技術などが求められています。

OKIサーキットテクノロジーは、進化し続ける半導体デバイスの確かな品質を、陰で支えている半導体テスト用プリント配線板をご提供いたします。

プローブカード

- 当社保有技術

- 半導体の微細化、多ピン化に対応した高精度、高多層基板をご提供いたします。

- 信号伝送の高速化による高品位電気特性に対応した、伝送線路シミュレーション技術

および特性インピーダンスの高精度コントロールを実現します。 - 同時並行設計、特別生産体制により、開発期間の短縮を実現します。

- 製品仕様

- 層数:4層~102層

- アスペクト比:25

- 最大外形:480×480mm

- 板厚:~6.8mm

- 材料:FR-4、HighTgFR-4

- 表面処理:無電解金めっき

パフォーマンスボード・DUTボード

- 当社保有技術

- 半導体の微細化、多ピン化に対応した高精度、高多層基板をご提供いたします。

- 狭ピッチ化(0.35㎜ピッチ)に対応した、高アスペクト基板をご提供いたします。

- 信号伝送の高速化による高品位電気特性に対応した、伝送線路シミュレーション技術

および特性インピーダンスの高精度コントロールを実現します。 - 同時並行設計、特別生産体制により、開発期間の短縮を実現します。

- 製品仕様

- 層数:4層~80層

- アスペクト比:25

- 最大外形:488×630mm

- 板厚:~7.5mm

- 材料:FR-4、HighTgFR-4

- 構成:シーケンシャル

- 対応実績FBGA:0.35mm、0.40mm、0.50mm

- 表面処理:無電解金めっき

バーンインボード

- 当社保有技術

- 多ピン化(1,000ピンクラス)に対応した、高集積大型多層基板をご提供します。

- 狭ピッチ化(0.4mmピッチ)に対応した、高精度大型基板をご提供します。

- 製品仕様

- 層数:2層~16層

- 最大外形:482×623mm

- 板厚:1.6mm ~

- 材料:FR-4、HighTgFR-4

- 構成:SVH、穴埋め対応可

- ソケットピッチ:0.40mm ~

- 表面処理:無電解金めっき、ソルダーコート、銅スルー

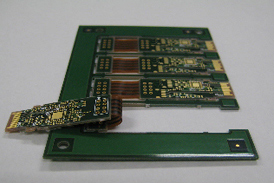

フレックスリジッド(F/R)のご提案

フレックスリジッドプリント配線板

2~8層のフレキ層(Zo制御も可能)なプリント配線板を実現します。

接続不具合、コネクタ接触抵抗、実装領域制限、コネクタ領域の確保、コネクタ取付け工数の問題を解消します。

F/R 2層

F/R 多層インナー

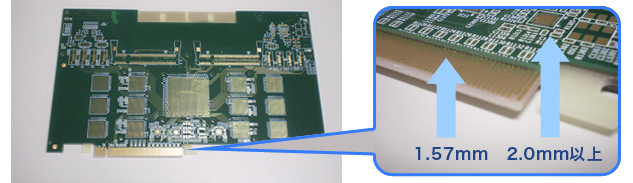

T-SEC-Board(複合板厚配線板)

T-SEC-Board

異なる板厚を1枚のプリント配線板で実現しました。

端子部分は板厚1.57mm(PCI-e規格)、高機能部品実装による高板厚2.0mm(例 FPGA搭載 18層以上)が共存できます。

T-SEC-Board(複合板厚配線板)