コラム

PCI Expressとは?

基板設計の際に注意すべきポイントを解説

PCI Expressとは何か?基本の理解

PCI Express(Peripheral Component Interconnect Express、略称:PCIe)は、パソコンやサーバーの内部で使用される高速なデータ転送インターフェース規格です。もともと1990年代のPCIバスを改良する形で開発されたこの技術は、現在のコンピューターシステムの核となる接続方式として広く採用されています。

PCIeの重要な特徴は、シリアル通信方式です。これにより複数のレーンを組み合わせてデータ転送速度の向上が可能になり、従来のパラレル通信方式に比べて高効率な通信が実現されています。

PCIeを利用する主な用途には、グラフィックスボード(GPU)・NVMe対応SSD・ネットワークカードなどが挙げられ、対象機器の性能を最大限に引き出す欠かせない規格となっています。

PCIeの技術的なメリット

PCIeには、現代のコンピューターシステムに必要不可欠な技術的メリットが下記の通りあります。

- 高速データ転送

- 柔軟な拡張性

- 低遅延

- 高信頼性

それぞれ詳しく解説します。

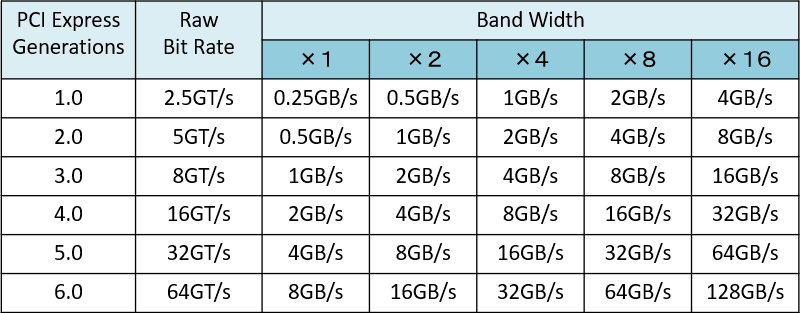

高速データ転送

高速データ転送は、圧倒的なデータ転送速度が最大のメリットといえます。PCIeは進化を続けており、世代ごとにデータ転送速度が大幅に向上してきました。たとえば、PCIe Gen4ではレーン1本あたり約16 GT/s(Gigatransfers per second)の速度を誇り、新しい世代のPCIe Gen5ではレーンあたり32 GT/sに達します。この高速性により、SSDやGPUといった高いスループットを必要とするデバイスの性能を最大限に活用できるでしょう。

PCIe 各世代と伝送レート

柔軟な拡張性

PCIeは設計の柔軟性により、多様な拡張カードやデバイスを接続できる点が大きな強みです。一つのPCIeソケットで必要に応じてレーン数を調整できるため、低帯域幅が求められるデバイスから高帯域幅を必要とするデバイスまで幅広く対応します。また、複数の接続を効率的に管理する「スイッチ」機構を利用して、PCIeデバイス間の接続を最適化し、単一のソケットで複数のデバイスを利用することも可能です。これにより、個々のユーザーが求める性能に応じた柔軟な構成を実現できます。

また、PCIeは下位互換性があり、たとえばPCIe 4.0対応のカードをPCIe 3.0スロットに挿入して使用できますが、転送速度は低い規格である3.0として動作します。さらに、物理的に小さいカード(×1など)を大きいスロット(×16など)に挿入して使用することも可能です。

低遅延・高信頼性

コンピューターシステムにおいて、遅延の最小化と信頼性の確保は非常に重要です。PCIeは高性能なエラーチェック機構を備えており、通信の整合性を維持するためにデータ送信中のエラー検知と再送を効率的に行います。この仕組みによって、データ転送の際のエラー発生率が非常に低く、高い信頼性を確保できます。さらに、シリアル通信方式により、従来の並列通信方式よりも遅延が抑えられており、リアルタイム処理が求められるアプリケーションや高負荷の計算処理にも最適です。これらの特性により、PCIeは産業用機器やハイエンドシステムでも信頼できるインターフェースとして広く利用されています。

基板設計におけるPCIe

PCIeは、高速・高性能な通信インターフェースとして、現代のコンピューターおよび電子機器の基板設計で中心的役割を果たしています。下記の通り、設計では効率的なレイアウトが重視されるほか、拡張性とスケーラビリティを確保するための工夫が求められます。

- 高性能な通信インターフェースとしての中核

- 拡張性とスケーラビリティの確保

- 高速化世代に対応するシミュレーション技術

それぞれわかりやすく解説していきます。

高性能な通信インターフェースとしての中核

PCIeは、前途のとおり最新世代のPCIe Gen5ではレーン1本当たり最大32 GT/sという驚異的な通信速度を実現しています。この性能を活かすには下記の観点が必要です。

- 基板設計段階で物理的制約や電気的制約を精密に最適化

- 規格が要求する信号品質・電源品質を確保

PCIeは差動信号を用いたシリアル通信が特徴的で、差動配線は構造上、外部ノイズに強く高速データ転送に適しています。PCIeでは各レーンが送信と受信のペアで構成されて全二重通信を実現します。そのため、これら配線の適切な設計が必要です。

拡張性とスケーラビリティの確保

PCIe基板設計では、システムの将来的な拡張に備えた柔軟性の確保が重要です。PCIeはレーン数(×1、×4、×8、×16など)によって帯域幅を拡張できる特性があり、設計時には将来的なレーン拡張の可能性を考慮した配線経路の確保が望ましいでしょう。

高速化世代に対応するシミュレーション技術

高速動作するPCIeを実装する基板では、予期せぬ動作不良の回避が必須です。基板設計段階で信号品質・電源品質に問題がないかシミュレーションを行い未然の検出・対策が重要です。昨今の高速信号を扱う基板開発において、シミュレーション適用は不可欠となっています。

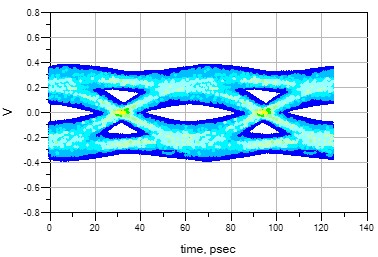

- SIシミュレーション:

PCIe Gen4以降などの10GT/sを超える世代では、反射による信号品質の劣化影響が大きくなるため、トレース以外の部品パッドやビアのインピーダンス整合が重要です。これらのインピーダンス整合条件の最適化には、3次元電磁界解析を用いたシミュレーションが必要とされ、基板特性を忠実に表現することが求められます。

その上で、基板モデルとIBIS-AMIなどのデバイスモデルを組み合わせて信号波形シミュレーションを行うことにより、PCIeの高速性能を最大限に引き出すことが可能です。

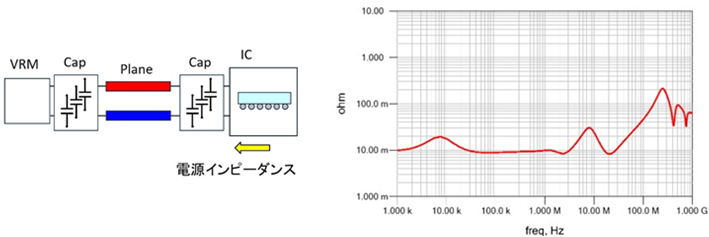

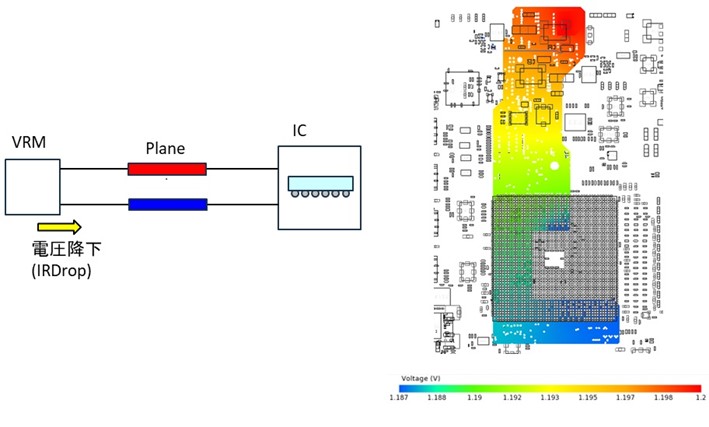

PCIe Gen4 信号波形 - PIシミュレーション:

各種CPUやFPGAは低電圧化、大電流化が進んでおり、これらデバイスが安定動作するためのマージンが減少しています。このため、電源品質の確保も基板設計段階で考慮すべき重要な項目です。PIシミュレーションで検証する主な項目としては、電源インピーダンス・電圧降下(IRDrop)があります。

電源インピーダンス解析 - 高速でスイッチング動作するデバイスを安定的に動作させる

キャパシタの容量や数量を最適化 電圧降下解析 - DCDCコンバータなど電源供給ICより供給される電源の電圧降下を検証

- 電源プレーンの幅や銅箔厚などが適切かを検証

電圧降下が大きい場合には電源プレーンを見直す

電源インピーダンス

電圧降下(IRDrop)

PCIeにおける基板設計の際に注意すべき4つのポイント

PCIeを基板設計に組み込む際は、通信品質や信頼性確保の観点で注意すべきポイントがいくつか存在します。下記の4つは特に重要な設計上の課題です。

- トレースの長さと整合性

- インピーダンス整合

- 電源供給とデカップリング

- EMI/EMC対策

それぞれのポイントを解説していきます。

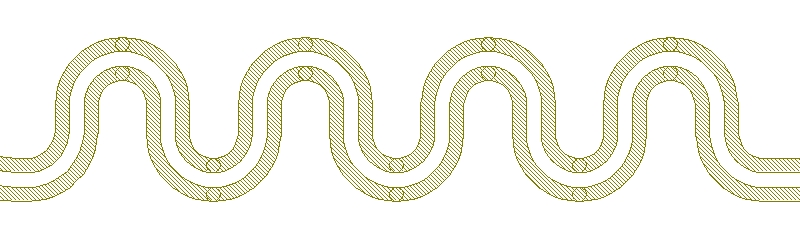

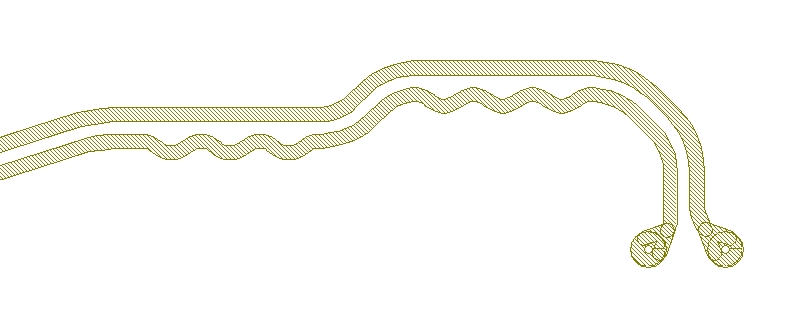

トレースの長さと整合性

PCIeは複数のレーンで並列にデータ通信を行うため、各トレースの長さが揃っていないと信号タイミングが乱れる原因となり、通信エラーが発生する可能性があります。この整合性を維持するには、基板上でトレースを均一な長さに調整する作業が不可欠です。一般的にミアンダ配線と呼ばれる、タイミングを調整するための折り畳み配線を行う際は、周囲の配線との結合を避けるため、近接する他の差動トレースとの間隙を保つ、および自身(同一ネット)の配線とも近接し過ぎないように注意が必要です。また、差動配線のPosi/Negaの配線長が異なると位相差を生じるため、Posi/Negaの差動ペア間の配線長も厳密に揃える必要があります。

ミアンダ配線

PCIeのミアンダ配線

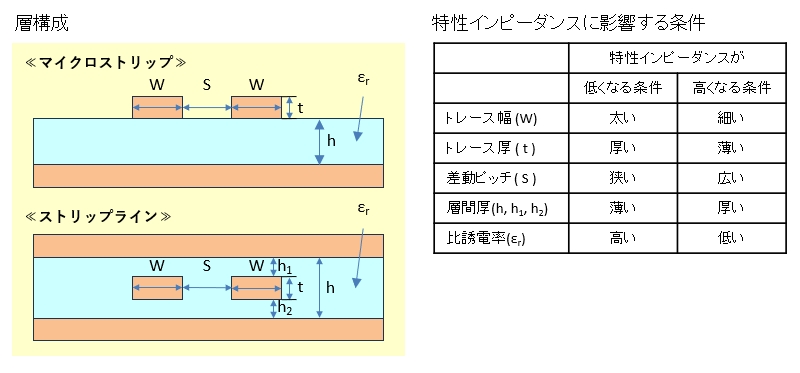

インピーダンス整合

高速信号であるPCIeのインピーダンス整合は、反射を最小限に抑え、信号の完全性を確保するために極めて重要です。PCIeでは通常、差動インピーダンスを85Ωまたは100Ωに管理することが求められます。

特性インピーダンスを決定する要因は下記の4つです。

- トレース幅および厚さ

- トレース間の距離(差動ペアのピッチ)

- 層構成(トレースとリファレンスとなるグラウンド層との距離)

- 基板材料(比誘電率)

基板設計者はこれらを考慮し、シミュレーションを活用して正確なインピーダンスの計算、調整することが大切です。

電源供給とデカップリング

PCIeの基板設計では、高速信号通信を実現するために安定した電源供給が不可欠です。デバイスの高速動作に伴い電源供給の安定性を確保するための電源配線設計とデカップリングが重要となります。

電源プレーンは、複数のデバイスに効率的に電源を供給しつつ、電源のスパイクノイズを抑える工夫が求められます。一方でデカップリングはPCIeデバイスの高速スイッチング動作に伴い急激に電流を要求する際に電圧変動を防ぐ役割を果たします。これらデカップリングコンデンサを適切に配置することで高周波成分を吸収し電源、信号品質の維持が可能です。

基板設計では、各デバイス近傍に適切な容量のコンデンサを配置し、電源回路が安定した電源インピーダンスを実現します。さらに電源プレーンの設計では、低インピーダンスとノイズ抑制を考慮した構造、レイアウトが推奨されます。

層構成とマイクロストリップ

EMI/EMC対策

高周波信号を使用するPCIeを実装する基板では、電磁適合性(EMC)に配慮した設計が不可欠です。基板設計時には下記の対策を講じます。

- 外部からのノイズの影響を防ぐために、信号トレースをシールド。

- 基板からの放射を抑制するために、高周波信号やクロック信号は内層に配線する、また基板の中央に配置。

- リターンパスの分断を避けるために、グランド層のスリットやビアのクリアランスによる分断を回避。

これにより、電磁干渉を最小限に抑え、他の電子機器の動作を妨げない設計が実現するでしょう。

問題を解決し基板性能を高める方法

PCIeは高性能な通信インターフェースである一方、高速信号を扱うため設計における課題が多く存在します。これらの問題を解決し、基板の性能を最大化するには、下記の2つが重要であると考えられます。

- 電源・グランド層の設計

- クロック信号の最適化

それぞれの方法について詳しく解説します。

この問題を解決し、基板性能を最大化するには、設計初期段階からの体系的なアプローチが不可欠です。

電源・グランド層の設計

PCIeデバイスは一般的に、大電流かつ安定した電力供給を必要とします。電源供給を行う基板の電源配線設計が不十分だと、電圧降下などの動作不良や熱問題が発生する可能性があるでしょう。プリント基板の電源設計では下記の注意が必要です。

- 電源プレーンの配置:基板内の電源供給部(DCDCコンバーターなど)から供給先の各デバイスの消費電流を考慮して、電源プレーンの幅、銅箔厚みを効果的に設定、配置

- グランド層の最適化:高速信号ラインのリターン電流経路、および、電源プレーンの低インピーダンス化、ノイズ抑制のためにグランド層の設計。

- デカップリングコンデンサの使用:デバイスごとに適切な容量、数量のデカップリングコンデンサを配置し、電圧変動やノイズの影響を最小化。電源プレーンとグランドプレーンが適切に設計されることで、PCIeの高信頼性を引き出せます。

クロック信号の最適化

PCIe信号の動作は、リファレンスクロックの精度に依存しています。不安定なクロック信号は通信エラーや性能劣化を引き起こすため、クロック信号の適切な設計と管理が重要です。具体的には下記を考慮します。

- 信号経路の最適化:クロック信号のトレースを最短距離で設計し、分岐が少ないレイアウトを構築することでノイズを抑制。

- ノイズ対策:必要に応じてシールドを設け、クロック信号ラインが外部ノイズに影響されないよう保護

- クロックジェネレーターの選定:安定性の高いクロックジェネレーターを選定し、基板全体の動作精度を向上

これらの対策により、PCIeの高速通信性能を維持しつつ、確実な動作を実現できます。

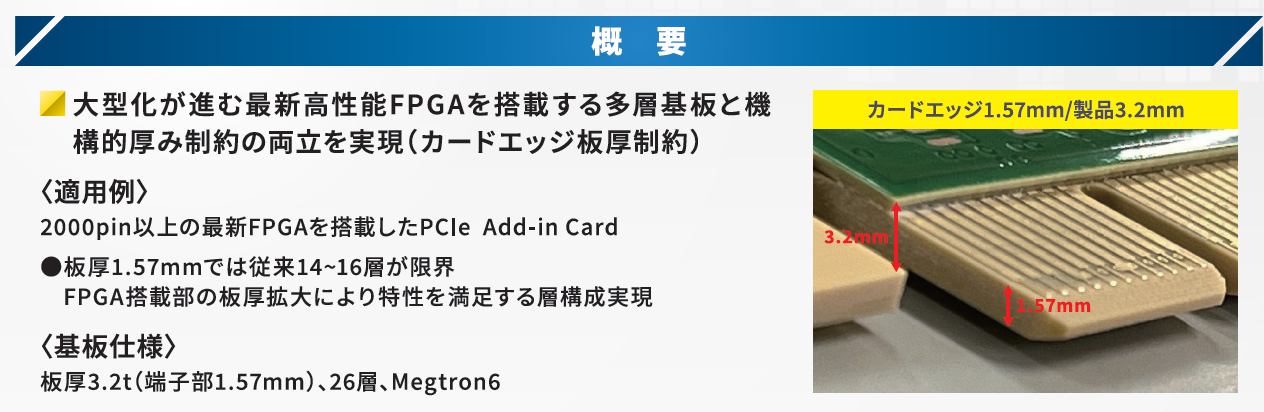

最新FPGAを搭載したPCleアドインカードの課題

最新FPGAを搭載したPCI eアドインカードは、AIアクセラレーション・HPC(ハイパフォーマンス・コンピューティング)・ネットワークなど処理性能の向上に重要な役割を果たしています。しかし、これらの用途で使用される高性能FPGAを搭載するプリント基板の設計には多くの課題が存在します。特に、多ピン化が進んだ最新FPGAでは、2000ピンを超えるパッケージが存在し、それに伴いプリント基板の信号層数を増やすことが必要です。この結果、PCIeアドインカードの板厚規格である1.57mmを維持することが困難になっています。

この課題に対して、当社では「複合板厚プリント基板」を提供しています。この構造では、カードエッジ部分の厚みを1.57mmに保ちながら、FPGAや高機能回路を搭載する部分では基板の厚みを3.2mmなど異なる厚みの設定が可能です。また、高速伝送に対応した低誘電基材(例:Megtron6/Panasonicなど)に対応しており、信号品質と高速性を両立させています。これにより、柔軟に最新で高性能なFPGA搭載のPCIeアドインカードを実現します。

まとめ

PCI eはその高速性、柔軟な拡張性、そして高信頼性の特性を持つことで、現代のコンピューターシステムにおける基幹技術としての地位を確立しています。技術進化のペースが速く、最新世代の標準化が進む一方で、歴代規格との互換性を維持しているという点に注目してください。

また、高速化が進むPCIeを実装するプリント基板設計には、注意点が多数存在します。これらを適切に管理することで、PCIeの性能を最大限に活かした高品質なプリント基板の実現が可能です。基板設計時にSI・PIシミュレーションを適用することで、未然に問題を検出し・対処ができるため、シミュレーションを活用した設計から取り組みましょう。

当社では多数の実績を保有しております。

お問い合わせ

フォームが表示されるまでしばらくお待ちください。

恐れ入りますが、しばらくお待ちいただいてもフォームが表示されない場合は、 こちらまでお問い合わせください。